“先进的数字处理器IC要求通过单独的DC参数和高速数字自动测试设备(ATE)测试,以达到质保要求。这带来了很大的成本和组织管理挑战。本文将介绍ADGM1001 SPDT MEMS开关如何助力一次性通过单插入测试,以帮助进行DC参数测试和高速数字测试,从而降低测试成本,简化数字/RF片上系统(SoC)的测试流程。

”作者:ADI产品营销经理Richard Houlihan、ADI产品应用工程师Naveen Dhull、ADI首席IC设计工程师Padraig Fitzgerald

先进的数字处理器IC要求通过单独的DC参数和高速数字自动测试设备(ATE)测试,以达到质保要求。这带来了很大的成本和组织管理挑战。本文将介绍ADGM1001 SPDT MEMS开关如何助力一次性通过单插入测试,以帮助进行DC参数测试和高速数字测试,从而降低测试成本,简化数字/RF片上系统(SoC)的测试流程。

图1.操作员将负载板安装到测试仪上,以测试数字SoC

ATE挑战

半导体市场在不断发展,为5G调制解调器IC、图像处理IC和中央处理IC等先进的处理器提供速度更快、密度更高的芯片间通信。在这种复杂性不断提高、需要更高吞吐量的形势下,保证质量成为当前ATE设计人员面临的终极挑战。其中一个关键性问题是:发射器(Tx)/接收器(Rx)通道数量不断增加,需要进行高速数字和DC参数测试。这些挑战令半导体测试越来越复杂,如果不加以解决,会导致测试时间更长、负载板更复杂和测试吞吐量下降。而在现代ATE环境中,也会致使运营费用(OPEX)增加,产出降低。

要解决这些ATE挑战,需要使用能在DC频率和高频率下运行的开关。ADGM1001能传输真正的0Hz DC信号,以及高达64Gbps的高速信号。这让人们得以构建高效的单个测试平台(一次插入),可配置为测试DC参数标准和高速数字通信标准,例如PCIe Gen 4/5/6、PAM4和USB 4。

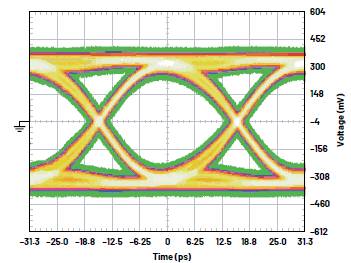

图2.ADGM1001眼图,32Gbps(RF1至RFC,包含参考波形,使用的伪随机测试码PRBS 215-1)。

如何测试HSIO引脚?

在高产量生产环境中测试高速输入输出(HSIO)接口是一大挑战。验证HSIO接口的一种常见方法是采用高速环回测试结构。这会将高速测试路径和DC测试路径集成在同一个配置中。

要执行高速环回测试,通常从发射器高速发射一个伪随机位序列(PRBS),在负载板或测试板上环回之后由接收器接收,如图3(左侧)所示。在接收端,对序列进行分析,以计算误码率(BER)。

图3.两种插入测试方法的示意图

DC参数测试(例如连续性和泄漏测试)在I/O引脚上进行,以确保器件功能正常。要执行这些测试,需要将引脚直接连接到DC仪器上,用该仪器施加电流并测量电压,以测试故障。

要在DUT I/O上执行高速环回测试和DC参数测试,可以使用多种方法来测试数字SoC;例如,使用MEMS开关或继电器,或使用两种不同类型的负载板,一种用于执行高速测试,另一种用于执行DC测试,这需要两次插入。

使用继电器执行高速测试和DC参数测试变得很有挑战性,因为大多数继电器的工作频率不超过8GHz,因此用户必须在信号速度和测试范围方面做出让步。此外,继电器体积大,会占用很大的PCB面积,这会影响解决方案的尺寸。继电器的可靠性一直备受关注,它们通常只能支持1000万个开关周期,这限制了系统的正常运行时间和负载板的寿命。

图3显示用于执行高速环回测试和DC参数测试的两种插入测试方法。图3中,左侧显示高速数字环回测试设置,其中DUT的发射器通过耦合电容接至接收器。图3右侧显示DC参数测试设置,其中DUT引脚直接连接至ATE测试仪进行参数测试。到目前为止,受组件限制,还无法在同一个负载板上同时提供高速环回功能和DC测试功能。

与两次插入测试相关的挑战

►管理两套硬件:用户必须维护和管理进行DC和环回测试所需的两套负载板。这使成本大幅增加,尤其是在测试大量器件时。

►延长测试时间,增加测试成本:两次插入测试意味着每个DUT必须测试两次,因此每次测试的索引时间将增加一倍,最终会增加测试成本,并显著影响测试吞吐量。

►测试时间优化:使用两套硬件时,测试时间无法优化。如果一个器件导致第二次插入失败,成本会进一步增加。第一次插入则会浪费测试仪时间。

►更易出现操作错误:由于每个DUT都要测试两次,出现操作错误的几率也会翻倍。

►解决方案设置× 2:两种测试插入方法涉及两组硬件,使得硬件设置时间翻倍。

►组织管理成本:两次插入测试,意味着需要移动更多组件。需要在两个测试仪之间,甚至两个测试室之间移动组件,带来了规划和组织管理挑战。

如何利用出色密度解决两次插入问题

ADI的34GHz MEMS开关技术采用小巧的5mm × 4mm × 0.9mm LGA封装,提供高速数字测试功能和DC测试功能,如图4所示。要执行高速数字测试,来自发射器的高速信号经由开关,路由传输回到接收器,在解码之后,进行BER分析。要执行DC参数测试,该开关将引脚连接到DC ATE测试仪进行参数测试,例如连续性和泄漏测试,以确保器件功能正常。在执行DC参数测试期间,MEMS开关还提供与ATE进行高频通信的选项,可以满足某些应用的需求。

图4.ADGM1001支持高速数字测试和DC测试(只突出显示P通道)

图5显示高速数字测试解决方案,分别使用继电器和使用ADGM1001 MEMS开关进行比较。使用MEMS开关时,解决方案的尺寸比使用继电器时缩减近50%,这是因为ADGM1001采用5 × 4 × 0.9mm LGA封装,比典型的继电器小20倍。PCIe Gen 4/5、PAM4、USB 4和SerDes等高频标准驱动多个发射器和接收器通道,这些通道需要紧密排布在PCB上,但不能增加布局复杂性,以消除通道与通道之间的差异。为了满足这些不断发展的高频标准的要求,MEMS开关在负载板设计中提供致密和增强功能,以便执行数字SoC测试。

图5.分别使用继电器和ADGM1001的环回解决方案比较

继电器尺寸通常很大,只能提供有限的高频性能。它们利用增强致密来支持更高的频率标准,例如PCIe Gen 4/5、PAM4、USB 4和SerDes。大多数继电器的工作频率不超过8GHz,在高频率下具有很高的插入损耗,会影响信号的完整性并限制测试覆盖范围。

ADGM1001简介

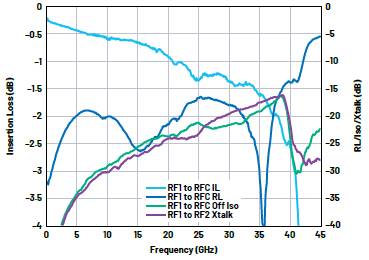

ADGM1001 SPDT MEMS开关在DC至34GHz频率范围内提供出色的性能。该技术具有超低寄生效应和宽带宽,开关对高达64Gbps信号的影响很小,并且通道偏斜、抖动和传播延迟都比较低,可实现高保真数据传输。它在34GHz时提供1.5dB的低插入损耗和3Ω低RON。它提供69dBm的良好线性度,可以处理高达33dBm的RF功率。它采用5mm × 4mm × 0.95mm小型塑料SMD封装,提供3.3V电源和简单的低压控制接口。所有这些特性使ADGM1001非常适合ATE应用,支持通过单次测试插入实现高速数字测试和DC参数测试,如图4所示。

图6.ADGM1001 RF性能

图7.封装类型:5mm × 4mm × 0.9mm 24引脚LGA封装

ADGM1001易于使用,为引脚23提供3.3V VDD即可运行。但是,VDD可以使用3.0V至3.6V电压。开关可以通过逻辑控制接口(引脚1至引脚4)或通过SPI接口进行控制。实现器件功能所需的所有无源组件都集成在封装内,易于使用并且节省板空间。图8所示为ADGM1001的功能框图。

图8.ADGM1001功能框图

使用ADGM1001实现单次插入测试的优势

►出色的高速和DC性能:实现从DC到34GHz的宽带宽是当今行业面临的挑战。ADGM1001的插入损耗、线性度、RF功率处理和RON等关键参数在DC到34GHz范围内都具有出色的性能。

►降低运营费用:

• 减少硬件数量:单次插入测试只需使用一套测试硬件;因此,用户无需投资购买两套硬件和测试设备,可以大幅降低运营费用。

• 测试仪的运行时间:与继电器相比,ADGM1001支持1亿个循环周期,提供出色的可靠性,可延长测试仪的运行时间,最终降低运营费用。

►提高测试吞吐量:ADGM1001允许使用单次插入测试,将索引时间减少一半,这会大幅缩短测试时间,提供更高的测试吞吐量和资产利用率。

►密集解决方案,面向未来:ADGM1001提供更高的致密度和增强功能。MEMS开关技术提供可靠的路线图,适用于DC至高频运行开关,且与不断发展的技术完全保持一致。

►降低组织管理成本:使用单次插入方法时,需要移动的组件数量更少,可以降低组织管理成本和规划难度。

►减少组件移动:使用单次插入测试方法时,DUT只需一次插入进行测试,减少了组件移动,最终可降低发生操作错误的几率。

结论

ADGM1001正在推动DC至34GHz开关技术的发展,使得组合使用高速数字和DC参数解决方案进行SoC测试成为可能。它有助于缩短测试时间,改善电路板设计布局(实现更高的DUT数量和吞吐量),并延长运行时间(提高可靠性)。

ADGM1001是ADI MEMS开关系列的新产品,可满足高速SoC测试需求。ADI的MEMS开关技术拥有可靠的发展路线,支持DC至高频的开关功能,适合面向未来的技术需要。

关于作者

Richard Houlihan投身电子行业25年,担任过设计、产品线管理、营销到业务部主管职位。他现在负责ADI公司先进的开关和多路复用器产品线的营销和业务开发。Richard利用自身在模拟前端结构方面的背景和广阔的市场渠道经验,负责督导战略创新和产品开发。他拥有都柏林三一学院的电气工程学士学位和波士顿东北大学的工商管理硕士学位。

Naveen Dhull于2011年获得爱尔兰沃特福德理工学院的电子工程学士学位。他于2011年加入ADI公司,担任IC布局工程师,随后于2016年调入开关和多路复用器应用团队。自2016年以来,他一直担任产品应用工程师,专注于使用CMOS和MEMS开关技术的RF开关。

Padraig Fitzgerald 2002年毕业于爱尔兰利默里克大学,获得电子工程学士学位。同年,他加入ADI公司爱尔兰利默里克分公司,担任固态开关评估工程师,2007年转向开关设计领域。Padraig完成了科克理工学院关于MEMS开关可靠性的研究硕士课程。他还拥有伦敦大学的金融和经济学硕士学位。他目前是精密开关部的首席设计工程师兼MEMS开关产品和器件设计人员。

分享到:

猜你喜欢