VIVADO EXPERT 系列 1 2017

高速设计收敛技术 Balachander Krishnamurthy

- ○高速设计挑战

- 。 设计分析

- o设计指南

- · 复杂性与拥塞分析

- ○总结

VIVADO EXPERT 系列

2017

## 高速设计挑战

- 高性能要求 (>400 MHz)

- 过晚发现问题

- RTL 编码风格

- 约束不彻底

- 逻辑层次过多

- 高扇出网络与控制集过多

- 次优时钟和大型块 (BRAM, DSP)

- 功耗与性能之间的权衡

- 复杂性与拥塞

- 时序收敛迭代过多

## UltraFast 设计方法 (UG949)

WHAT WHERE

WHY

HOW

ANSWERS

- 进行综合后迭代以实现更快速的分析与可预测的结果

- RTL 编码风格与实例

- 在所有方面以检查表方式提供建议:

- 单板和器件规划

- 设计创建

- 实现

- 设计收敛

- 运行"Report Methodology"以尽快确定问题并解决问题

- 综合、时序、XDC 及时钟方法检查

### UG1231: UltraFast 设计方法快捷参考指南

#### UltraFast Design Methodology Quick Reference Guide (UG1231)

#### INTRODUCTION

The UltraFast™ Design Methodology is a set of best practices recommended by Xilinx to maximize productivity and reduce design iterations of complex systems, including embedded processor subsystems, analog and digital processing, high-speed connectivity, and network processing. See the UltraFast Design Methodology Guide for the Vivado Design Suite {UG949} for more information.

The UltraFast Design Methodology Checklist (XTP301) includes common questions that highlight typical areas where design decisions have downstream consequences and draws attention to potential problems that are often unknown or ignored. It provides easy access to related collateral. The checklist is available within the Xilinx Documentation Navigator tool (DocNav).

This quick reference guide highlights key design methodology steps to achieve quicker system integration and design implementation and to derive the greatest value from Xilinx\* devices and tools. Pointers to related collateral are also provided. The main design tasks covered in this guide include:

- Board and Device Planning

- Design Entry and Implementation

- Top-Level Design Validation

- Design Analysis

- Design Closure

Refer to the UltraFast Design Methodology – System-Level Design Flow available within the Xilinx Documentation Navigator tool (DocNav) for pointers to all design hubs and specific collateral.

UG1231 (v2016.3) November 11, 2016

#### BOARD AND DEVICE PLANNING

#### **PCB** Designer

#### Examine Key Interfaces

Validate part orientation and key interfaces

#### Examine the PCB Layout

- Perform the Memory Interface and Transceiver Checklists

- Follow PCB layout recommendations

- Ensure final FPGA pinout is signed off by FPGA designer

#### Review the Schematic

- Complete PC8 Checklist review

- Check PDS, configuration, and power supplies

- Validate I/O state before, during, and after configuration

#### Manufacture and Test

Verify the configuration sequence, power supplies, and I/O performance with the test I/O project

#### See Also:

UG949: Board and Device Planning

PCB Design Checklist

Memory Interface IP Design

Checklists

Schematic Design Checklists

#### **FPGA Designer**

#### Analyze Device for Pinout

- Examine transceiver and bonded I/O locations

- Examine SSI technology I/O planning

- Validate part orientation and key interfaces

#### Define I/O Pinouts for Key Interfaces

- Create I/O planning projects

Define and validate memory controllers, GTs, and PCIe\*

- technology locations

Establish a clocking skeleton

- Establish a clocking skeleton

- Minimize floorplan distance between connected IP

#### Define Final Pinout

- Merge interface projects into a final I/O project

- Validate DRCs and SSN analysis

- Implement design to check clocking and I/O rules

- Use the final I/O project for production test

#### Estimate Power

- Determine power budget and thermal margin using Xilinx Power Estimator (XPE)

- Apply toggle rates using knowledge of prior designs

#### See Also:

UG949: Board and Device Planning Power Estimation and Optimization Design Hub 1/O and Clock Planning Design Hub

#### DESIGN ENTRY AND IMPLEMENTATION

#### **Logic Designer**

#### Define a Good Design Hierarchy

- Define relevant hierarchies to help global placement and floorplanning

- Insert I/O and clock components near the top level

- Add registers at main hierarchical boundaries

- . Generate IP and review target device utilization

#### **Build and Validate RTL Submodules**

- Ensure design adheres to RTL coding guidelines

- Add sufficient registers around DSP and memories

- Use control signals only when absolutely necessary

- Use synthesis attributes to control final logic mapping

- Create simple timing constraints to review estimated timing and address paths with too many logic levels

- Review synthesis log files, utilization report, and

- elaborated view to identify sub-optimal mapping

Run Methodology and RTL checks and review issues

- Implement the submodule in out-of-context (OOC) mode to validate implemented performance

- Review utilization and power against original budget

- Simulate the design to validate functionality

#### Assemble and Validate Top-Level Design

- Synthesize the top-level RTL design and resolve all connectivity issues

- · Review top-level utilization and clocking guidelines

- Create and validate top-level constraints

- Iterate the RTL and constraints to fix Methodology and DRC issues and meet timing

- Proceed to implementation

#### See Also:

UG949: Design Creation and Implementation.

Designing with IP Design Hub

Using IP Integrator Design Hub

Logic Synthesis Design Hub

Applying Design Constraints Design Hub

Implementation Design Hub

# 设计分析

约束、逻辑层次、控制集与高扇出网络

## 基线 - 彻底的约束

#### ■ 基线: 确保时序约束彻底

- 要定义所有时钟及时钟关系

- 要正确约束异步跨时钟域

- ▶1 位 CDC: 伪路径或时钟组约束

- ▶多位 CDC: 使用 set\_max\_delay datapath\_only 和/或 set\_bus\_skew

- IO 约束

- 其他点对点例外约束

#### 优化槽调路沿

## 逻辑层次

- 检查逻辑层次数量

- 指南: 每个逻辑层次 500 ps (1 个 LUT + 1 个网络)

- 分析时使用:

report\_design\_analysis - logic\_level\_distribution -extend

- 建议:

- · 修改 RTL 以减少逻辑层次的数量

- 使用基于实例的综合来优化模块

- ▶综合选项: 重定时、区域、性能、可布线性等。

| 速度等级           | -1    | -2    | -3    |

|----------------|-------|-------|-------|

| 7 系列           | 575ps | 500ps | 425ps |

| UltraScale     | 490ps | 425ps | 360ps |

| UltraScale+    | 350ps | 300ps | 250ps |

| UltraScale+ LV | 490ps | 425ps | 360ps |

## 基于实例的综合选项

■ 使用 XDC 实现基于实例的优化

set\_property BLOCK\_SYNTH. RETIMING 1 [get\_cells U1]

set\_property BLOCK\_SYNTH. STRATEGY {ALTERNATE\_ROUTABILITY} [get\_cells U2]

set\_property BLOCK\_SYNTH. STRATEGY {AREA\_OPTIMIZED} [get\_cells U3]

set\_property BLOCK\_SYNTH. LUT\_COMBINING [get\_cells U3/inst1]

- 支持嵌套选项

- 以预置为策略

- 允许多个逻辑选项

基于实例的综合设置

默认 占位面积 性能 可布线性 重定时 adder threshold comparator threshold shreq min size fsm extraction lut\_combining flatten\_inside\_partition extract\_partition flatten hierarchy control set threshold max\_lut\_input muxf\_mapping keep\_equivalent\_register 适用于实例的策略

策略

(捆绑预置)

逻辑选项

**EXILINX** > ALL PROGRAMMABLE.

和逻辑选项

## 控制集

使用report\_utilization 和 report\_control\_sets -verbose进行分

- 控制集会影响布局和时序

- ■指南

- 如果唯一控制集的数量不足 slice 总数的 7.5%, 则可以接受

- 如果唯一控制集的数量超过 slice 总数的 15%, 则需要进行分析

### ■ 建议

- 手动复制高扇出寄存器或使用 PhysOpt

- 利用全局综合选项更改默认值 (-control\_set\_opt\_threshold)

- ▶ 根据架构使用不同阀值

- ✓ 7 系列使用的阈值为 4, UltraScale 和 UltraScale+ 使用的阈值为 2

- 在架构内实现时序关键低扇出(<8)控制信号

- ➤ 在 RTL 中使用 extract\_enable 或 extract\_reset

- ➤ 在 XDC 文件中:

set\_property extract\_enable/reset "no" [get\_cells U1/tmp\_reg]

```

module top (input clk,

input [9:0] din, a, b

(* extract_enable = "no" *)

output reg [9:0] dout);

reg [9:0] dinr, ar, br;

wire en = ar = br;

always @(posedge clk)

begin

ar <= a;

br \le b;

dinr <= din:

if (en)

```

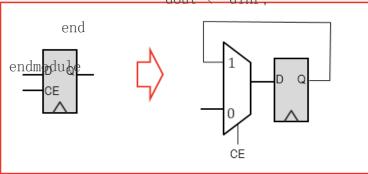

逻辑位于 D 输入侧的 CE 仿真

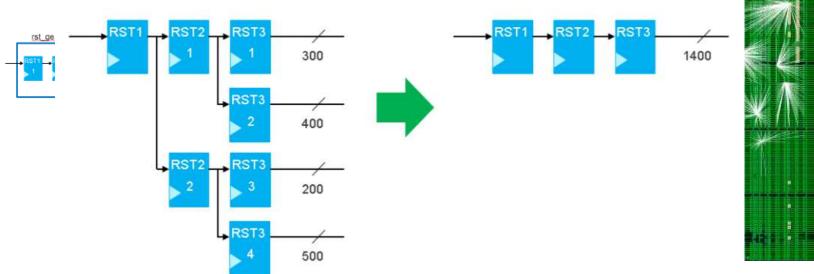

## 高扇出网络

运行report\_high\_fanout\_nets 进行分析

#### ■ RTL 建议:

- 如果不是关键时序,而且高扇出网络直接馈送 FF

- ▶ 将扇出 >25k 的网络推广到全局时钟

set\_property CLOCK\_BUFFER\_TYPE BUFG [get\_nets netName]

- 时序关键

- ▶ 使用 KEEP 属性在 RTL 中复制寄存器

- ▶ 使用 pblock 约束在每个 SLR 中进行复制

- 避免高扇出进出 DSP/BRAM

#### ■ 综合建议:

- 避免将 MAX\_FANOUT 用于全局控制信号

- 如果需要,只在小模块内使用 MAX\_FANOUT

- 使用 PhysOpt 复制高扇出网络驱动器

- Phys\_opt\_design -force\_replication\_on\_nets

- Phys\_opt\_design -directive AggresiveExplore

## 高扇出网络优化流程

- 综合: 受限复制

- 避免将 MAX\_FANOUT 用于全局控制信号

- 如果需要,只在小模块内使用 MAX\_FANOUT

- 在手动复制单元上使用 KEEP

- Opt Design: 粗粒度复制

- 基于大设计层级

- Place Design: 中粒度复制

- 基于早期布局和时序信息

- Phys Opt Design: 精细粒度复制

- 基于精确时序信息

## Opt Design 中的高扇出网络优化

#### Opt Design

- 在高扇出网络上插入、合并与分割 BUFG (默认执行)

- 使用 '-control\_set\_merge' 合并 opt\_design 中的低扇出控制信号

- 使用 '-merge\_equivalent\_drivers'合并所有 LUT 和 Flop 等效驱动器

- 使用 '-hier\_fanout\_limt <number>'控制基于模块的复制

## 布局器中的高扇出网络优化

- 布局器中的物理综合 (PSIP)

- 在全局布局过程中根据资源可用性自动插入 BUFG

- 布局过程中使用'-fanout\_opt'复制高扇出网络

- 复制连接到 DSP/BRAM 的低/中扇出网络

- 优势

- 不需要在 RTL/综合层面进行猜测

- 理想的控制集使用

- 布局已知, 而且复制基于驱动器和负载布局

- 在布局器中较早解决时序关键的 HFN

- 减少布局后的物理优化

### PSIP 实例:控制信号

■ 大型 BRAM 的 FF 驱动地址位

Without replication in placer WNS = -0.312 ns

With replication in placer WNS = 0.146 ns

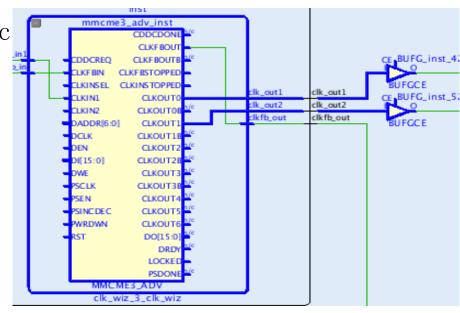

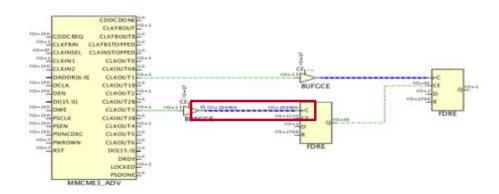

### 设计指南 时钟、同步 CDC、BRAM 和 DSP

### 时钟指南

- 次优时钟损害时序

- 对时钟方法检测进行检查并修复

- 尽可能减少时钟缓冲器的利用率

- 通过组合相同的同步时钟来减少时钟数

- 从 MMCM 反馈路径移除缓冲器 (不支持延迟补偿)

- 除非绝对需要, 否则移除级联缓存

- 当处在 INTERNAL 模式,从 MMCM 反馈路径移除缓冲器

- 布局规划要保留的时钟

- 接近驱动器的低扇出时钟

- 远离高利用率区域

- 避免使用在结构资源上布线的时钟

- 不可预测的偏差,与其他网络在布线资源上的竞争

- 负载超过 30 时,尽量插入时钟缓存器

### 同步 CDC 指南

### ■ 分析关键交叉

- 运行 report\_timing\_summary 或 report\_clock\_interac

- 严格的设置要求(对偏差更敏感)

- 最大数量的路径(对 TNS & THS 影响最大)

### ■ 检查并改善 CDC 时钟拓扑结构

- 配置 MMCM 的 VCO 以便在最高频率下运行

- > 降低时钟不确定性

- 在 MMCM 之前避免公共节点

- 避免级联缓存

- 避免跨越 IO/SLR 边界以最大限度降低偏差

### ■减少/放松 CDC 路径

- 作为异步处理(需要正确的同步电路)

- 使用多周期路径约束(放松设置) (需要 CE 逻辑)

## 同步 CDC 中的时钟偏差

CLOCK\_DELAY\_GROUP 约束可限制同步时钟偏差

- 匹配组内时钟网络延迟

- 用于约束同步 CDC 偏差

- 与使用 USER\_CLOCK\_ROOT 约束相比精度更高

- 实例:

set\_property CLOCK\_DELAY\_GROUP group\_0 [get\_nets {u1/c1k\_50M u1/c1k\_100M}]

#### ■指南

- 适用于直接连接至缓冲器输出的网段

- 缓冲器必须具有相同的驱动单元 ⇒ 确保平衡的拓扑结构 ➤ 驱动器实例: MMCM、PLL、IBUFDS、GT CHANNEL

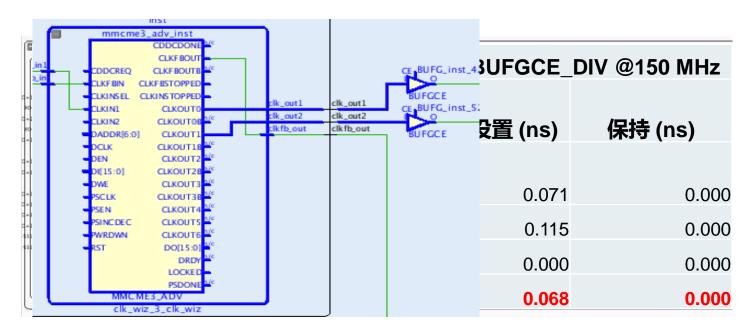

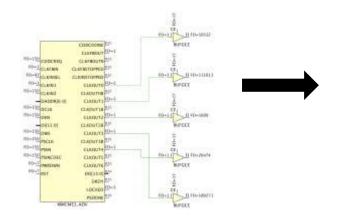

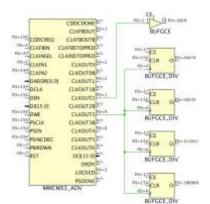

## 利用 UltraScale 器件中的 BUFGCE\_DIV

- 使用 BUFGCE\_DIV 以执行分频

- 移除相位误差(~120ps) => 有助于设置和保持 CDC 路径

- 具有简单周期比的时钟 (/1 /2 /4 /8)

- 每个时钟区域仅有 4 个 BUFGCE\_DIV

- 注意 BUFGCE 与 BUFGCE\_DIV 之间的单元延迟差异

- 两个时钟最好使用相同的缓存类型(BUFGCE\_DIV 可除以 1)

## 真实客户设计 - 案例研究

- 使用高速时钟及多个同步 CDC 进行设计

- 使用 report\_clock\_interaction 确定关键 CDC 路径(预布线)

| Source Clock  | Destination Clock | WNS (ns) | TNS (ns) | Failing Endpoints<br>(TNS) | Total Endpoints<br>(TNS) | Path Req<br>(WNS) | WHS (ns) | THS _ 1 (ns) | Failing Endpoints<br>(THS) | Total Endpoints<br>(THS) | Path Req<br>(WHS) | Common<br>Primary Clock | Inter-Clock<br>Constraints |

|---------------|-------------------|----------|----------|----------------------------|--------------------------|-------------------|----------|--------------|----------------------------|--------------------------|-------------------|-------------------------|----------------------------|

| svs clk 491   | svs_clk_491       | 0.165    | 0.000    | 0                          | 430480                   | 2 034             | -0.253   | -289 459     | 10007                      | 430480                   | 0.000             | Yes                     | Partial False Path         |

| sys_clk_245   | sys_clk_491       | 0.916    | 0.000    | 0                          | 3292                     | 2.034             | -0.383   | -271.798     | 2022                       | 3292                     | 0.000             | Yes                     | Partial False Pat          |

| sys_clk_491   | sys_clk_245       | 0.420    | 0.000    | 0                          | 3751                     | 2.034             | -0.206   | -254.735     | 2687                       | 3751                     | 0.000             | Yes                     | Partial False Pat          |

| svs_clk_245   | sys_clk_122       | 0.461    | 0.000    | 0                          | 1125                     | 4.069             | -0.224   | -73.057      | 619                        | 1125                     | 0.000             | Yes                     | Partial False Pati         |

| sys_clk_245   | sys_clk_61_44     | 10.444   | 0.000    | 0                          | 3134                     | 16.276            | -0.234   | -70.723      | 868                        | 3134                     | 0.000             | Yes                     | Partial False Path         |

| sys_clk_245   | sys_clk_245       | 0.255    | 0.000    | 0                          | 238146                   | 4.069             | -0.234   | -46.686      | 1802                       | 238146                   | 0.000             | Yes                     | Partial False Path         |

| sys_clk_30_72 | sys_clk_61_44     | 9.222    | 0.000    | 0                          | 5348                     | 16.276            | -0.430   | -41.222      | 545                        | 5348                     | 0.000             | Yes                     | Partial False Path         |

| svs_clk_30_72 | svs_clk_122       | 27.186   | 0.000    | 0                          | 12908                    | 32 552            | -0.356   | -33,333      | 415                        | 12908                    | 0.000             | Yes                     | Partial False Path         |

| svs_clk_122   | sys_clk_245       | 0.540    | 0.000    | 0                          | 10781                    | 4 069             | -0.185   | -21.341      | 580                        | 10781                    | 0.000             | Yes                     | Timed                      |

| sys_clk_122   | sys_clk_61_44     | 10.212   | 0.000    | 0                          | 1083                     | 16.276            | -0.196   | -14.464      | 172                        | 1083                     | 0.000             | Yes                     | Timed                      |

- 找出具有最严格设置要求和最高 THS 违规的 4 个时钟

- 改善时钟树并应用 CLOCK\_DELAY\_GROUP

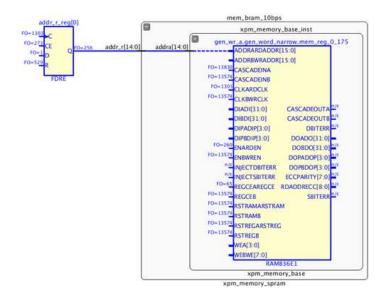

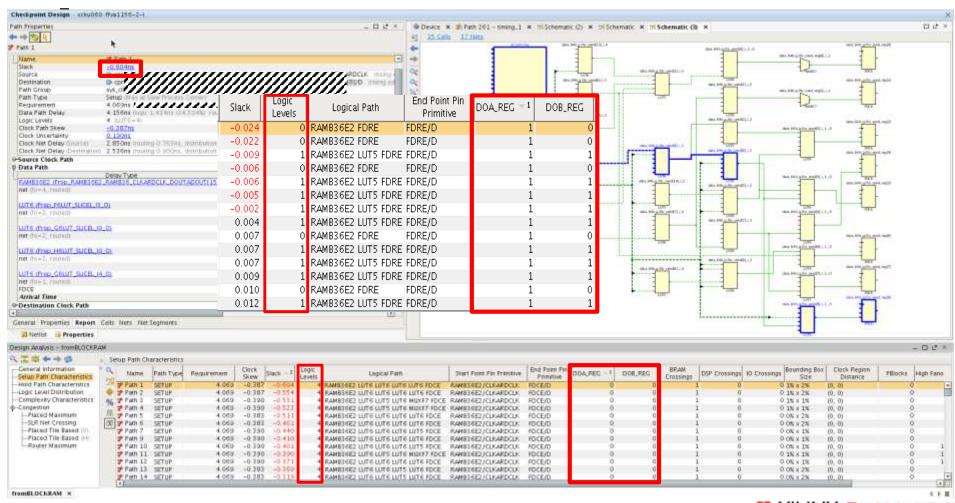

### 块 RAM

进出块 RAM 的路径指南

- 在 LUTRAM(〈8kb)中实现更小的存储器

- 避免高扇出信号进出大型块

- 使用 KEEP 属性根据层级在 RTL 中进行复制

- 2016.3 提供整个流程的高级复制特性

- 使用 low-logic-level 路径以驱动控制信号

- 根据需要复制地址总线或使用 PhysOpt

- 针对性能/功耗, 建议使用 cascade height 属性

- 针对高性能设计启用输出寄存器

- 寄存器应位于内部或直接连接到输出引脚

- 使用 report\_design\_analysis 分析 块 RAM 路径

```

report_design_analysis -of_timing_paths [get_timing_paths \

-from/to [get_cells -hier -filter {PRIMITIVE_GROUP==BLOCKRAM}] \

-max 1000 -nworst 16 -unique_pins] -file <from><to>BLOCKRAM.rpt

```

```

(* ram_style = "distributed" *)

reg [31:0] mem [(2**8)-1:0];

reg [7:0] addr_reg;

...

(* ram_style = "block",

cascade_height = 1/8/32 *)

reg [31:0] mem [(2**15)-1:0];

reg [14:0] addr_reg;

...

```

## 真实客户案例研究 - 未寄存的 RAMB 输出

■ 来自相同 RAMB 的众多路径在 250MHz 时具有 4 个以上的逻辑级

# 复杂性与拥塞

## 设计复杂性

使用 report\_design\_analysis -complexity 进行分析

- 复杂性衡量逻辑互连程度

- 复杂模块可能处于层级中靠下的几级

- 更改 GUI 中的'Hierarchical depth'

更大实例上的高 Rent、高平均扇出

| `           |                                                                 | 1.4                              | 4/44                 | —                    |                        |                  |                    | П                | 町 Lu              | 110%              | 一同          | MOVL       | ጥ ጥ! | 川中      |      |

|-------------|-----------------------------------------------------------------|----------------------------------|----------------------|----------------------|------------------------|------------------|--------------------|------------------|-------------------|-------------------|-------------|------------|------|---------|------|

| ∢ Ci        | omplexity Characteristics                                       |                                  |                      |                      |                        |                  |                    |                  |                   |                   |             |            |      |         |      |

| ) Q         | Instance                                                        | Module                           | Rent -1              | Average<br>Fanout    | Total<br>Instances     | LUT1             | LUT2               | LUT3             | LUT4              | LUT5              | 1175/6      | MemoryLUT  | DSP  | RAMB    | MUXE |

| -           | P-N utop                                                        | utop                             | 0.51                 | 2.73                 | 38637                  | 701              | 3507               | 2932             | 3016              | 3957              | 6128        | 1585       | 68   | 80      | 1025 |

| , 🕽         | —                                                               | mgtTop                           | 0.27                 | 1.80                 | 1198                   | 48               | 48                 | 154              | 144               | 72                | 44          | ^          | ^    |         | ^    |

| <b>₽</b> •  |                                                                 | or1200_top                       | 0.52                 | 3.78                 | 10308                  | 137              | 598                | 879              | 792               | 928               | 2461        | 416        | 4    | 22      | 312  |

| :           |                                                                 | fftTop                           | 0.68                 | 124                  | 3315                   | 34               | 1151               | 56               | 42                | 12                | 116         | 769        | 64   | 0       | 0    |

| 40.         |                                                                 | usbf_top                         | 0.70                 | 4.12                 | 11414                  | 241              | 845                | 913              | 1015              | 1374              | 1717        | 200        | 0    | 29      | 331  |

| %           |                                                                 | usbf_top_0                       | 0.71                 | 4.12                 | 11414                  | 241              | 845                | 913              | 1015              | 1374              | 1717        | 200        | 0    | 29      | 331  |

| ₩<br>•<br>% | oruEngine (or1200_top) fitEngine (fftTop) subEngineO (usbf_top) | or1200_top<br>fftTop<br>usbf_top | 0.52<br>0.68<br>0.70 | 3.78<br>1.34<br>4.12 | 10308<br>3315<br>11414 | 137<br>34<br>241 | 598<br>1151<br>845 | 879<br>56<br>913 | 792<br>42<br>1015 | 928<br>12<br>1374 | 116<br>1717 | 769<br>200 | 0    | 0<br>29 |      |

育 LITCO 育 MIVC→ 利田家

- 目的

- 在布局之前找出具有高 rent (>0.65) 和/或高平均扇出 (>4.0) 的高难度模块 (>15k 个单元)

- 解决方案

- 选项 1: 尝试不同综合选项,采取从下到上的综合流程(00C)

- 选项 2: 布局规划高难度模块

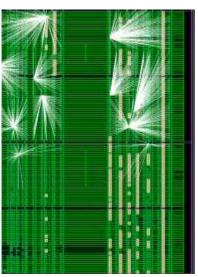

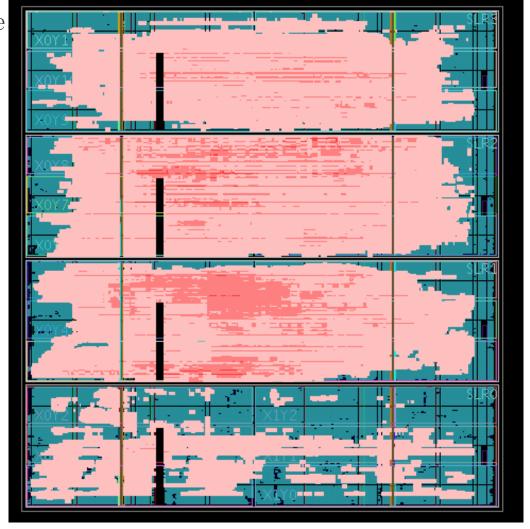

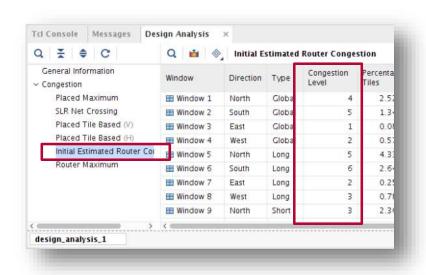

### 拥塞 使用 report\_design\_analysis -conge

### ■ 具有以下特点的物理区域

- 高引脚密度

- 布线资源高利用率

#### ■ 具有拥塞感知能力的布局器:

- 平衡拥塞、走线长度、时序的关系

- > 并非总是能够消除拥塞

- > 因保持修复而无法预计拥塞

- ▶时序估算受绕路影响

- 报告通过布局器看到的拥塞区域

### ■布线器拥塞

- 可通过迂回布线处理拥塞,但会影响时序

- 报告布线率接近100%的区域

"Smear" 图

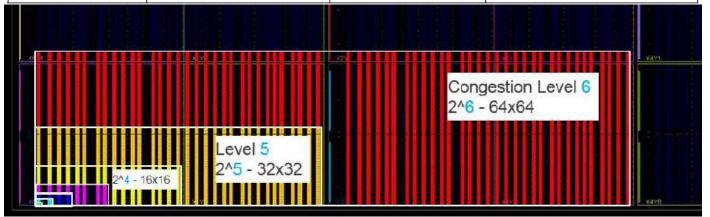

## 拥塞级别

### ■ 定义

- 拥塞级别相当于包含拥塞布线的正方形区域的大小

- 正方形大小基于互连 (INT\_XnYm) 或 CLB (CLE\_M\_XnYm)

### ■ 拥塞级别范围

| Level | Area             | Congestion | QoR Impact               |

|-------|------------------|------------|--------------------------|

| 1, 2  | 2x2, 4x4         | None       | None                     |

| 3, 4  | 8x8, 16x16       | Mild       | Possible QOR degradation |

| 5     | 32x32            | Moderate   | Likely QOR degradation   |

| 6     | 64x64            | High       | Difficulty routing       |

| 7,8   | 128x128, 256x256 | Impossible | Likely unroutable        |

### 拥塞类型

- Global: 布线资源利用率高的区域

- 与供应相比, 进出该区域的连接需求较高

- 常见原因: 高度 LUT 合并、控制集过多、大量总线、布局规划较差

- 更详细的模型通常有利于 UltraScale和UltraScale+ 的分析: Short 和 Long

- Short: 缺少短距离布线: SINGLE、DOUBLE、QUAD

- 在 UltraScale 中更常见

- 常见原因: MUXF 或 CARRY 原语的高密度集中

- Long:缺少长距离布线: HLONG、VLONG

- 在 UltraScale+ 中更常见

- 常见原因: 模块的 Rent/平均扇出较高,大型块的高利用率(强连接性),过多 SLR 交叉网络

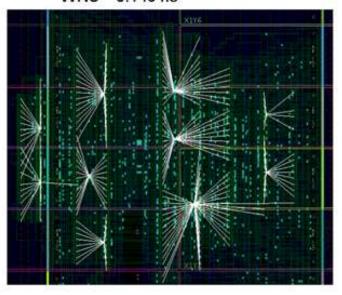

## 拥塞分析: 建议方法

警告: [Route 35-447] 拥塞正阻止布线器对所有网络进行布线。

- 检查布线器警告消息

- 运行报告设计分析 (IDE) 或 report\_design\_analysis -congestion

- 关注初始估算布线器拥塞

- ▶最详细的报告: Global、Long 和 Short 拥塞

- ▶在初始布线后布线器所见的拥塞图片

- ▶纳入有效更改的最佳时机

- 布局报告确认拥塞, 但不够精确

- Router Maximum 表明拥塞是否解决

- 检查初始估算布线器拥塞等级

- 4 级及以下 通常没有问题

- 5 级 有一定难度,但如果是隔离区域可以解决

- 6 级 布线难度极大,影响编译时间和 Fmax

- 7 级及以上 通常不可能

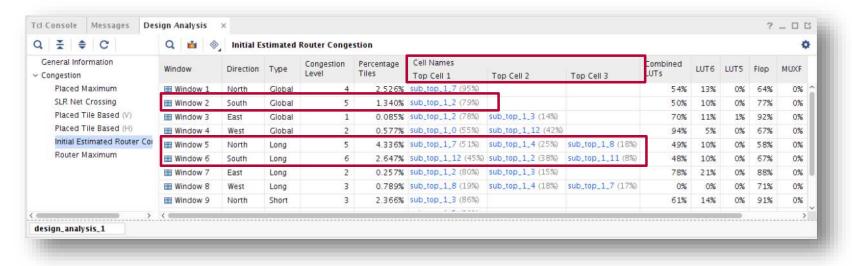

## 针对 UltraScale 和 UltraScale+ 的拥塞分析

■ 找出造成拥塞区域的层级单元

- 检查这些单元中的拥塞"症状"

- report\_design\_analysis -congestion: 检查利用率列

- report\_design\_analysis -complexity: 使用 -hierarchical\_depth 报告单元复杂性标准

- report\_qor\_suggestions: 评估分析结果并在问题区域应用建议方案

- report\_utilization [-cells]: 检查问题单元的利用率

## 导致拥塞的罪魁祸首

- 拥塞区域可能因网表结构形成

- 大量使用 MUXF 会导致连接短缺

- 长 CARRY 链引起密集逻辑和连接

- 大量低扇出控制信号(复位、使能)消耗布线资源

- 过量的复杂逻辑 cone (高 Rent 指数)

- 对造成拥塞的层级单元进行重新综合

- 注意: 全局使用策略和选项,可能会对时序造成更广泛的影响

- 使用块级综合策略以生成更合适的网表

- 无关联(00C)流程可用于尚未由块级综合处理过的解决方案

### 拥塞解决方案 (1/2)

- 禁用问题实例上的 LUT 组合

- 在实现的最初阶段使用空值覆盖现有的 LUT 属性

```

set_property HLUTNM "" get_cells -hier -filter {ref_name = LUT* && name = */inst/*}

```

- MUXF 和 CARRY 原语的高利用率可能会导致拥塞

- 使用 opt\_design 将 MUXF 和 CARRY 原语重新映射到 LUT

- 全局选项 -muxf\_remap 和 -carry\_remap: 可能会影响时序,要谨慎使用

- 使用单元属性MUXF\_REMAP 和 CARRY\_REMAP 关注拥塞区域内的单元 set property MUXF REMAP 1 [get cells inst a]; # opt design only remaps MUXF cells in inst\_a

- 进一步降低逻辑层次以最大程度减小时序影响

- opt\_design -remap: 影响整个设计

- 可以使用 DONT\_TOUCH 进行精准优化

```

set orig_dont_touch_cells [get_cells -hier -filter DONT_TOUCH]; # remember which cells have DONT_TOUCH set DONT_TOUCH 1 <all cells except those to be remapped>; # isolate the cells for optimization opt_design -remap; # only optimize the isolated cells set DONT_TOUCH 0 [get_cells -hier]; # removed DONT_TOUCH from all cells set DONT_TOUCH 1 $orig_dont_touch_cells; # restore original DONT_TOUCHed cells

```

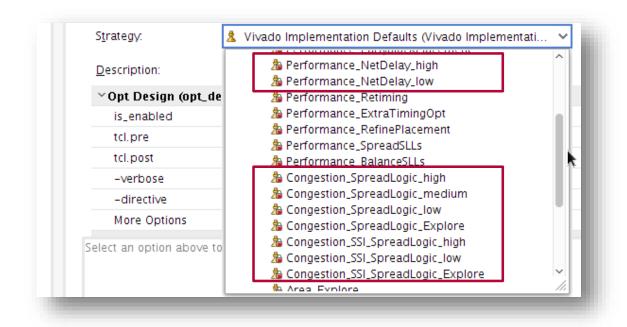

## 拥塞解决方案 (2/2)

■ 建议实现策略

UltraScale+: NetDelay\* 是不错的选择 更少的 Short 拥塞, 更多的 Long 拥塞

UltraScale: SpreadLogic\* 是较好的选择

请参阅 UG904 附录 C, 查看用于 每个策略的指令

# report\_qor\_suggestions (RQL)的

- 分析设计中的 QoR 问题并推荐解决方案

- 可以在任意设计阶段运行

- 报告有悖于不同 QoR 检查的设计问题

- 针对每个设计问题推荐要采取的行动

- 提供包含建议修复措施的交钥匙 XDC 和 Tc1 文件

- 下一个阶段朝自动时序收敛解决方案方向发展

- 当前格式: 包含详细描述和补充文件的文本报告

- 未来版本: 交互式 GUI 报告

- 最终目标: 设计收敛向导

# 总结 减少时序收敛迭代

- 高速设计提出很多挑战

- 分析 →根本原因 → 解决方案

- 使用 Vivado 强大的分析功能

- 尽早分析并修复设计问题

- 运行、检查并修复所有方法检测

- 检查逻辑层次、控制集和高扇出网络

- 依照指南缓解拥塞

- 强大的优化技术

- 使用高级综合与实现指令及策略

- PhysOpt 布局后、布线后

## 附加资源

- ➤ UG 949➤ UG 903➤ UG 906现在均可在资源工具集中找到!

- **▶** UG 1231

- ➤ Vivado Design Suite 的 UltraFast 设计方法 简介与概览

- ➤ Quick Take 视频 约束爆炸

- ▶ 时序收敛的 Vivado UltraFast 设计方法

- > china. xilinx. com/vivado

#### Chinese

http://i.youku.com/xilinx

**XILINX**

ALL PROGRAMMABLE,

http://weibo.com/xilinxchina

http://forums.xilinx.com/cn

### **English**

facebook.com/XilinxInc

twitter.com/#!/XilinxInc

youtube.com/XilinxInc

linkedin.com/company/xilinx

plus.google.com/+Xilinx

xilinx.com/about/app-download.html